追求存储密度以降低存储成本不断推动着NAND闪存技术的发展。NAND闪存技术已经从最初的SLC时代,跨越MLC、TLC向QLC时代快速演进,并且从最初的2D平面技术全面切换到3D堆叠技术。而3D NAND闪存技术也从最初的32层堆叠,发展到了目前最新一代的高达128层堆叠。

随着NAND存储密度不断提高,SSD主控芯片的纠错码(ECC)设计面临着极大挑战。一方面,伴随着NAND存储密度提高,闪存的数据可靠性严重恶化,SSD主控芯片的ECC技术也完成了从最初的BCH技术向先进的LDPC纠错技术的全面迁移。特别是进入QLC时代之后,NAND闪存存储介质需要SSD主控芯片进一步提供更高的错误比特纠正能力。另一方面,具有高纠错能力的先进LDPC纠错技术设计复杂度高,带来了主控芯片功耗的急剧上升,给SSD系统稳定性带来了极大隐患。而且LDPC复杂的解码过程,特别是软解码,会大量占用闪存数据带宽,从而降低SSD用户实际使用性能,还会严重恶化数据读写延时,带来极差的用户体验。因此,为了适应NAND闪存技术的发展,ECC纠错技术研究一直是SSD主控芯片厂商核心竞争力之一。

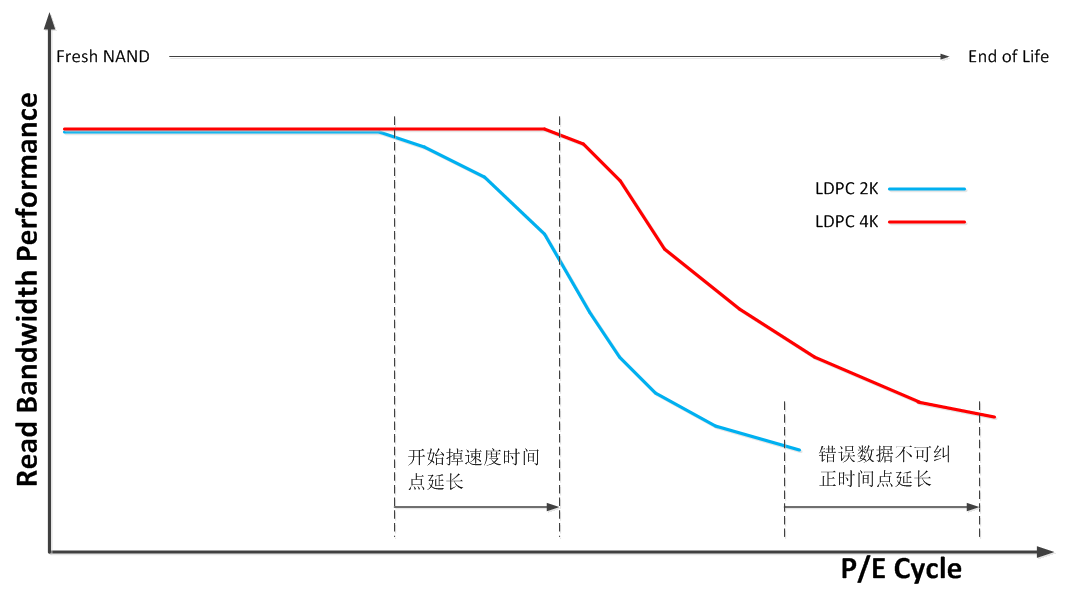

图1:4K LDPC极大延长NAND使用寿命

联芸的Agile ECC技术是基于先进ECC的NAND闪存信号处理技术,能大大提升闪存数据的可靠性并极大延长SSD的寿命。近日,联芸科技在基于2K LDPC纠错的 Agile ECC 2技术基础上进行二次技术创新,成功实现了基于4K LDPC纠错的第三代Agile ECC 3闪存信号处理技术的开发和验证。据联芸科技高管表示,联芸科技即将推出的新一代SSD主控芯片将全面启用4K LDPC纠错技术,这也是国内SSD主控芯片厂商第一次实现该技术的连续突破,从最初的技术跟随到实现技术超越的一次蜕变,必将引领SSD主控芯片技术创新发展,未来4K LDPC纠错技术必将成为SSD主控芯片必备的关键核心技术。

相比2K LDPC纠错技术,4K LDPC纠错性能无论是硬解码还是软解码都有大幅提升。在相同原始误码率(RBER)情况下,相对于2K LDPC,4K LDPC的纠错失败概率(UFER)能降低至少两个数量级。或者说在相同纠错失败概率(UFER)要求下,4K LDPC能容忍更高的闪存颗粒原始误码率(RBER),从而可以大大延长闪存的使用寿命。

联芸的Agile ECC3技术引入4K LDPC,无论是硬解码能力还是软解码能力相比2K LDPC都有极大提升。LDPC软解码的能力提升保障了最恶化情况下的闪存数据可靠性,极大的延长了SSD的使用寿命;而LDPC硬解码能力提升则可以大大减少进入LDPC软解码的概率,从而避免了复杂的LDPC的软解码过程,大大提升了用户实际使用体验。原则上LDPC码长从2K到4K会增加电路实现复杂度,带来芯片功耗的增加和成本上升。但是联芸科技4K LDPC纠错技术采用独特的LDPC编解码器架构和先进的动态功耗管理技术,大大优化了系统功耗和成本。联芸基于4K LDPC的第三代Agile ECC技术过一系列技术创新,不但大大提升了主控芯片的闪存纠错能力,还优化芯片功耗,给用户带来极佳的性能和超低功耗体验。

扫一扫,获取最新资讯!

我的评论

最新评论