三星电子宣布,已开发出业界首个12层3D-TSV((Through Silicon Via)技术。

三星新的创新被认为是大规模生产高性能芯片的最具挑战性的封装技术,因为需要通过超过60,000多个TSV孔的三维结构垂直互连12个DRAM芯片。

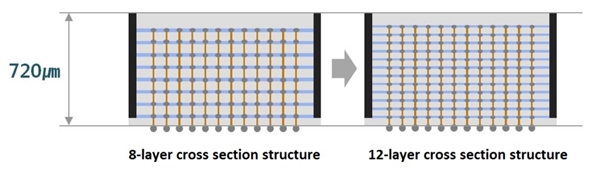

*PKG cross section structure

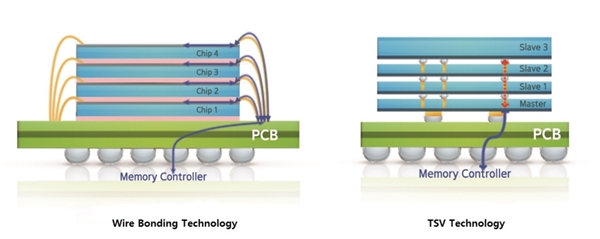

*Wire bonding vs TSV technology

封装的厚度与当前8层高带宽存储器HBM2产品相同,这是在组件设计上的一项重大进步,将帮助客户研发具有更高性能和容量的下一代大容量产品,而无需更改变系统配置设计。

此外,3D封装技术还具有比当前现有的引线键合技术短的芯片间数据传输时间,从而显着提高了速度并降低了功耗。

三星电子TSP(测试与系统封装)执行副总裁Hong-Joo Baek表示:“随着各种新应用(例如人工智能(AI)和高功率计算(HPC)),确保超高性能存储器的复杂性的封装技术变得越来越重要。随着摩尔定律的扩展越来越接近极限,预计3D-TSV技术的作用将变得更加关键,三星将在最新的芯片封装技术上走在前沿。”

凭借其12层3D-TSV技术,三星将为数据密集型和超高速应用提供高性能的DRAM,三星计划将很快投入24GB批量生产(16Gb x 12 layers),其容量是当今市场上8GB(8Gb x 8 layers)高带宽存储器的三倍。

三星将凭借其尖端的12层3D TSV技术满足快速增长的大容量HBM解决方案市场需求。

我的评论

最新评论