说到高速,大部分业内反应的都是颗粒品质和传输协议,在海量和计算流的未来里,只要涉及逻辑运算能力和实时获取信息并做出决策,一定会想到“高速”、“CPU”、“NAND”、“DRAM”这几个关键词,在大数据时代,这几个关键词代表了核心,但是今天这篇文给大家介绍一下晶体管技术。

晶体管的发展

从CMOS技术的角度来看,除了通用逻辑和功率器件产品外,还存在NOR闪存技术。对于25nm以下的DRAM,NAND和逻辑产品,它们的晶体管已分别发展为环绕栅晶体管(SGT),环绕栅(GAA,GAAFET)和鳍式场效应晶体管(FinFET)。

主流晶体管和产品应用的最新发展

低于1 Xnm的3D NAND FLASH是由垂直电流GAA存储器组成,FinFET的电路逻辑已逐渐从CMOS演变为二维增强结构,与multi-fins或者MBCFET并联,以增加电流大小,以上技术都需要更高级的光刻机来完成,例如深紫外线DUV或者极紫外光EUV。

存储节点技术和密度的提高取决于两项关键技术:新兴材料和创新结构。由新兴材料(例如FRAM,MRAM,PRAM和RRAM)衍生的存储器已经被少数制造商制造和使用。

GAA的局限性

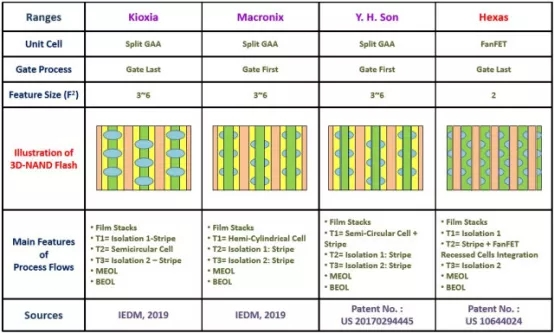

观察这四个存储单元的主要区别(此处省略了GAA工艺),前三家公司使用的GAA单元拆分制造模型是基于GAA工艺的。从GAA单元变为椭圆形后,技术上将其拆分为Split GAA单元。

3D-NAND闪存单元形成的主要特征比较

上面的四家公司具有相似之处,包括垂直电流,具有多层堆叠的工艺技术,连接单条导线,位线和字线的方式。在外观上看似相似,Hexas存储器当前操作区域的结构与前三个明显不同。

为了执行存储单元模块的处理,必须将前三个单元固定为一定的值才能满足随后的处理。泡孔的直径是Split GAA泡孔的短轴之一,会影响最终密度。然而,FanFET存储单元模块在工艺集成中没有这样的问题,因为FanFET存储单元的单元形状和特征尺寸可以根据开发者的需求自由地调整,并且可以有效地改变密度。上述三个公司的特征尺寸是大约3.5F 2〜6F 2,因为单元电池本身是闭环结构,和帧间细胞和小区内之间的隔离层都必须符合设计规则。

此外,由于先栅极和后栅极工艺等各种工艺的顺序和差异,隔离层和单元的串联以及工艺流程上的薄膜残留物和CD偏压可能会导致不同程度的边际效应。

拆分GAA可能存在严重问题,即它是单位单元中的闭环结构,并且这种结构可能会限制单位单元的大小。当晶胞收缩时,将面临填充介电层膜和BL的问题。同时,拆分GAA单元将增加功能部件的大小,从而导致单位面积的内存密度降低。

扫一扫,获取最新资讯!

我的评论

最新评论

2020-07-13