继2020年年初JEDEC固态技术协会发布第三版HBM2存储标准后,在近日公布了下一个主流内存标准 DDR5 SDRAM的最终规范,这项标准满足了密集型云和企业、数据中心等应用领域驱动的需求要求。

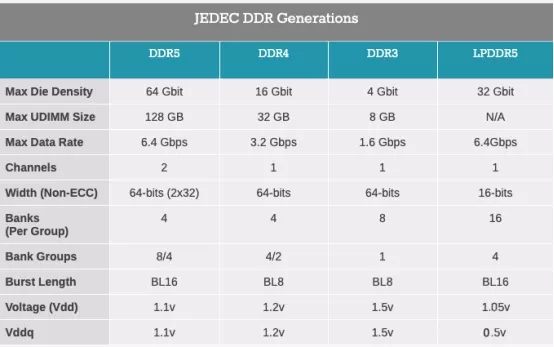

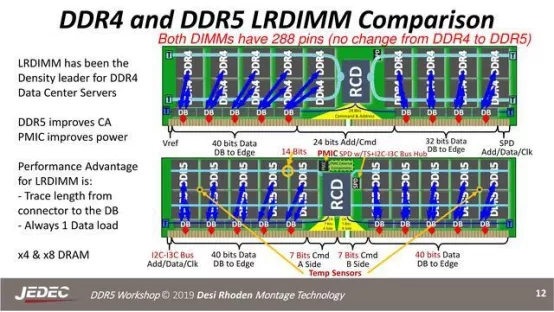

根据Anandtech报道,和之前的每一次DDR迭代一样,DDR5的主要关注点再次放在提高内存密度以及速度上。JEDEC希望将这两方面都提高一倍,最高内存速度将达到6.4Gbps,而单条LRDIMM的容量最终将能够达到2TB,最大UDIMM容量为128 GB。同时,还有一些较小的变化,以支持这些目标或简化生态系统的某些方面,如on-DIMM电压调节器以及on-die ECC。

DDR 5是DDR标准的最新迭代,每个版本的DDR都相对应的影响着整个市场,涉及了企业服务器,PC,以及其他产品。

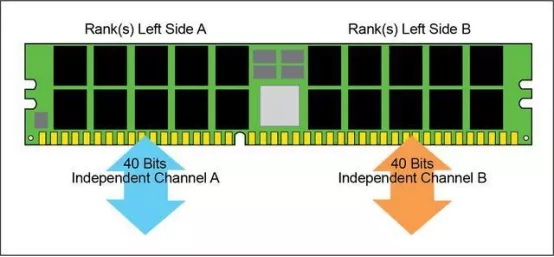

一个模块,两个通道

DDR5的出现,满足了包括客户端系统和高性能服务器在内的各种应用中对高效能不断增长的需求。通过利用并扩展了行业知识和开发先前DDR内存的经验,在不降低通道效率的情况下以更高的速度扩展内存性能,这是通过将突发长度加倍到BL16,将存储体计数从16增加到32来实现的。

这种革命性的体系结构提供了更好的通道效率和更高的应用程序级别性能这将使下一代计算系统得以持续发展。此外,DDR5 DIMM在同一模块上具有两个40位完全独立的子通道,以提高效率并提高可靠性。

快速总线服务

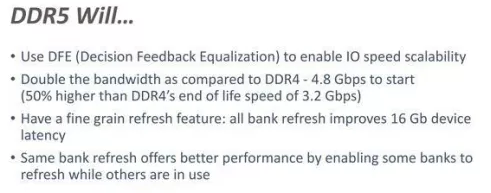

DDR 5的DFE功能(决策反馈均衡)功能可以实现IO速度可扩展性,实现更高的宽带和更高的性能,DDR5的带宽是其DDR4的两倍,预计将以4.8 Gbps的速度推出(比DDR4的3.2 Gbps使用寿命快50%)。

DFE是一种通过使用来自内存总线接收器的反馈来提供更好的均衡效果来减少 inter-symbol 干扰的方法。更好的均衡又可以使DDR5内存总线以更高的传输速率运行所需的更清晰的信号传输,而不会发生任何故障。同时,标准中的一些较小更改进一步帮助了这一点,例如添加了新的改进训练模式,以帮助DIMM和控制器补偿内存总线上的微小时序差异。

DDR5内存之所以拥有更快的内存带宽,是因为对DIMM的内存总线做出了修改,以便在每个时钟周期内传输更多的数据。除以上的改动外,JEDEC 还对DIMM的工作电压进行了一定的调整。相比DDR4的1.2V来说,DDR5降低至1.1V,以便玩家充分压榨内存的工作频率。

这里最大的变化是命令和地址总线正在收缩和分区( shrunk and partitioned),其引脚被重新分配给第二个存储通道的数据总线。DDR5将具有两个7位CA总线,而不是单个24位CA总线,每个通道一个。

大厂蠢蠢欲动

JEDEC预计DDR5将在硬件完成后的12到18个月内开始出现在终端设备中,并从那里开始增加。尽管该小组没有提供具体的产品指导,但他们非常清楚地表示,他们希望服务器再次成为早期采用的推动力,尤其是在大型超大规模产品方面。

在固态技术协会JEDEC内存规范之后,英特尔、AMD、镁光、三星、海力士等行业巨头均提出相关计划,海力士表示将在年内量产DDR5内存颗粒,而AMD和英特尔将着手准备支持DDR5内存的服务器平台,明年发布的AMD EPYC 3平台以及英特尔的Eagle Stream平台都极有可能首发DDR5内存。

随着DDR 5的准备发布,企业端,数据中心和服务器市场端将会迎来怎样的变化?国内市场目前刚刚铺开DDR 4,工厂产线是否需要更换设备?欢迎评论区留下你的看法。

扫一扫,获取最新资讯!

我的评论

最新评论