HBM(High Bandwidth Memory)是一种专为数据密集型应用程序设计的特殊DRAM,通过先进的封装技术(如TSV硅通孔技术)将多个DRAM芯片垂直堆叠,实现高容量、高带宽、低延时与低功耗。它作为数据的“中转站”,能提升图像处理和渲染速度,显著增强系统性能,优化功耗,并减小封装体积。HBM在高性能计算、图形处理、数据中心和人工智能等多个领域得到广泛应用,市场前景广阔。

数据显示,2023年HBM仅占DRAM输出的一小部分,但预计未来几年将以50%的复合年增长率增长。存储大厂美光预测,到2025年,HBM DRAM市场规模有望突破250亿美元大关。在2024至2025年间,HBM产品或将面临供不应求的局面。此类需求增长正在推动对DRAM晶圆处理设备及其相关能力的需求的增长,设备大厂应用材料预计其HBM封装收入将在2024财年增长多达6倍,达到6亿多美元。

不过,领导厂商虽对市场持乐观态度,但业界也传出不同的声音——当前HBM供应状况良好,但预计到了2025年,实际产量可能会逐步逼近甚至超越当前被视为过高的市场需求水平。

生成式AI催生对于高速存储需求

十余年前,超微半导体(AMD)与SK海力士(SK Hynix)开业界之先河,共同推出HBM初代产品,即HBM1。HBM技术采用了硅通孔(TSV)技术,实现了多层die堆叠,从而提供了远超传统内存的高带宽和低功耗性能。这一创新使得HBM成为GPU等带宽需求较高的处理器的理想选择。

AI大模型运算之所以需要HBM,主要基于以下四点:首先,AI大模型具有庞大的参数和复杂的计算结构,需要处理大量数据,而HBM的高带宽和容量能有效支持其数据处理需求;其次,HBM能提供更高的带宽,释放AI加速器如GPU的硬件性能,提升运算速度和效率;第三,HBM具有较低的功耗,有助于降低系统能耗和散热压力,确保长时间稳定运行;最后,HBM的高可靠性和稳定性能满足复杂应用场景下的数据存储需求,确保数据完整性和安全性。

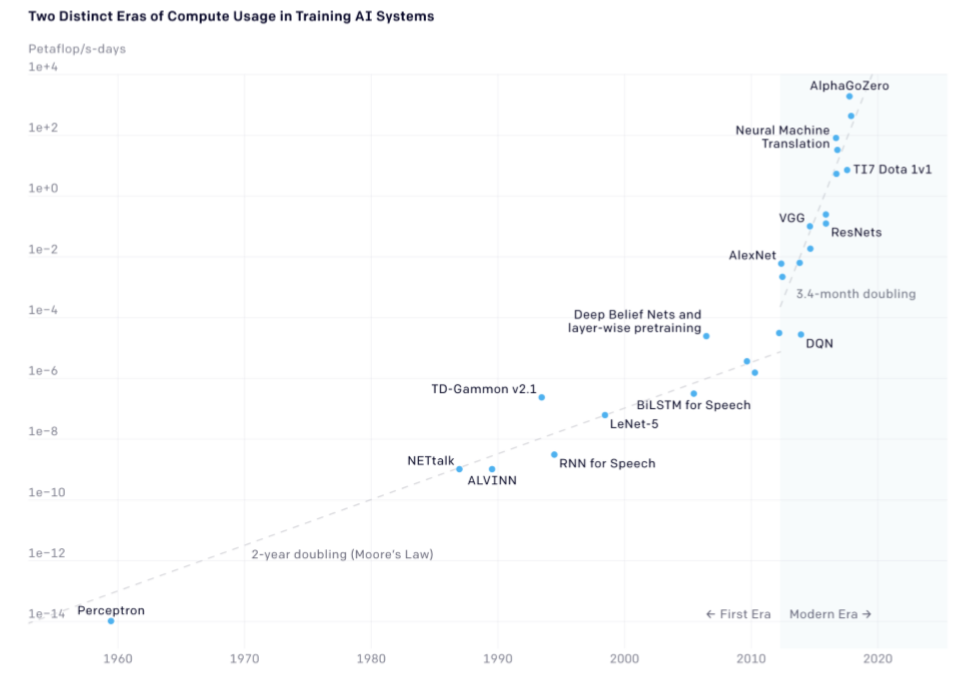

图片来自openai

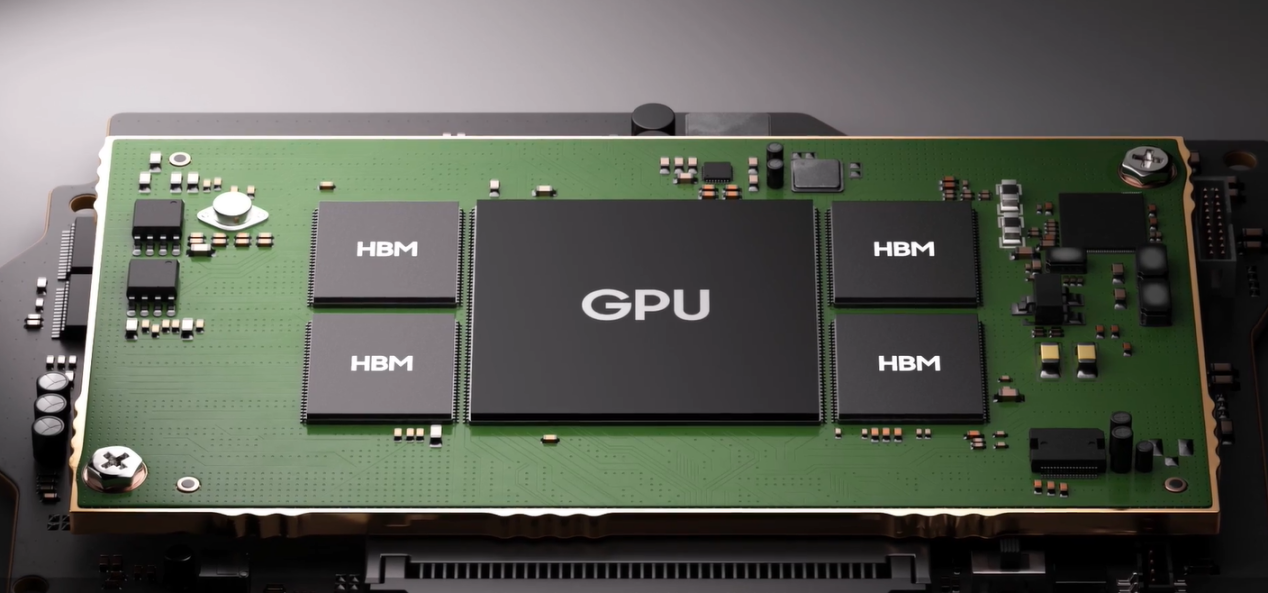

凭借在GPU(图形处理器)领域的深厚底蕴和技术领先地位,当前AI大模型的模拟与训练主要依赖的加速卡大多源自英伟达,其主打产品涵盖A100、H100、H200系列,以及V100、Tesla T4、Tesla P40、Tesla M60等其他型号的加速卡。

不过,尽管英伟达在AI加速卡市场占据领导地位,其他厂商并未止步,同样在积极研发。如AMD推出的MI300X和MI325X等已在市场上获得良好反馈。(国内厂商如华为等也推出了自家的AI加速卡产品,以满足不同场景的AI计算需求。)

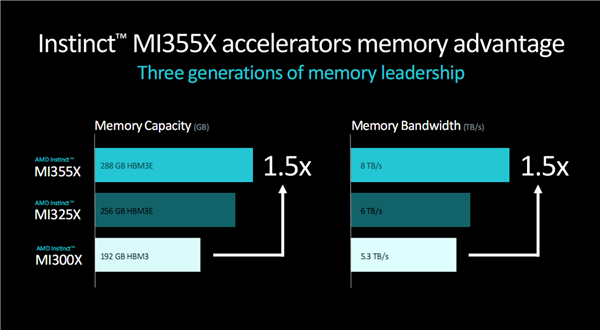

尤其值得一提的是,在北京时间11日凌晨,AMD宣布推出配备256GB HBM3E内存(为MI300的1.8倍)、带宽高达6TB/s的MI325X加速卡。同时,AMD还宣布了MI350系列的首款产品MI355X,采用先进的3nm工艺,配备288GB HBM3E内存,带宽更是飙升至8TB/s。这不仅显示出AMD在AI加速卡领域的强劲实力,同时也让HBM应用再度受到关注。

图片来自于AMD

HBM领域“三国杀”

随着技术的不断发展,HBM已经迭代到了更先进的版本,如HBM2、HBM2E、HBM3以及HBM3E等。各大产厂商的技术持续迭代,不断让HBM在性能上有了显著的提升,堆叠层数、数据传输速度、带宽以及容量等方面均得到了优化。

美光

今年2月,美光(Micron)宣布已开始批量生产其HBM3E高带宽内存。该产品采用TSV封装、2.5D/3D堆叠技术,首批产品为8-Hi设计,提供24GB容量和超过1.2TB/s的带宽,后续还推出了12-Hi堆栈版本,单颗容量增至36GB,带宽保持不变。其针脚速率超过9.2Gb/s。该厂商宣称,与竞品相比,其功耗降低了约30%。

该产品的推出满足人工智能加速器、超级计算机和数据中心的苛刻需求。该厂商表示,其HBM3E将应用于英伟达H200 Tensor Core GPU等产品,产品正在进行英伟达认证,并已向主要行业合作伙伴运送量产产品进行测试。

图片来自美光

之后于9月,美光宣布推出HBM3E 12层堆栈36GB存储器。该厂商表示,与目前的 HBM3E 8 层堆栈 24GB 产品相比,其HBM3E 12层堆栈36GB存储器,较8层堆栈的24GB产品提升50%,能支持大型AI模型在单处理器上运行,减少通讯延迟。与竞品相比,其功耗大幅降低,同时提供每秒超过1.2TB/s的带宽和每秒超过9.2Gb的Pin速度,以最低功耗实现最大吞吐量。

AI系统制造非常复杂,HBM3E 整合需要存储器供应商、客户和外包半导体封装测试(OSAT)厂商之间的密切合作。TSMC 生态系统和联盟管理部门负责人 Dan Kochpatcharin 评论道:“作为 OIP生态系统的一部分,双方密切合作,使美光以 HBM3E为基础的系统和基于CoWoS封装设计能够帮助客户进行AI创新。”目前,美光是台积电(TSMC)的 3DFabric 联盟的重要合作伙伴。

Sk海力士

在2013年首次在业界推出第一代HBM(HBM1),至今年9月底,SK海力士宣布全球率先量产12层堆叠HBM3E。此新产的运行速度提高至现有内存的最高速度9.6Gbps,其是在以搭载四个HBM的单个GPU运行大型语言模型(LLM)‘Llama 370B’3时,每秒可读取35次700亿个整体参数的水平。该厂商通过堆叠12颗3GB DRAM芯片,实现容量提升50%而厚度不变,采用更薄的DRAM芯片和TSV技术。同时,应用先进MR-MUF5工艺解决结构性问题,提升放热性能10%,增强稳定性与可靠性。

三星

三星在2023年10月举办的Samsung Memory Tech Day 2023活动中,首次宣布了代号为Shinebolt的新一代HBM3E。

今年2月底,三星成功发布了其首款采用12层堆叠技术的HBM3E DRAM,命名为HBM3E 12H。这款产品在持续运行状态下能提供最高达1280GB/s的带宽,并且存储容量达到了36GB。与三星之前推出的8层堆叠HBM3 8H相比,HBM3E 12H在带宽和存储容量上均实现了超过50%的大幅提升。

图片截取三星宣传视频

另外,近期业界传闻指出,在高性能存储芯片(如HBM)领域,三星电子相较于SK海力士等已略显落后;而在定制芯片外包生产方面,三星又落后于台积电。这种激烈的市场竞争态势限制了三星电子在芯片业务方面的利润空间。根据三星最近公布的2024年第三季度财报,由于竞争对手增加了对传统产品的供应,三星电子的内存芯片业务盈利能力出现下滑。

HBM工艺革新

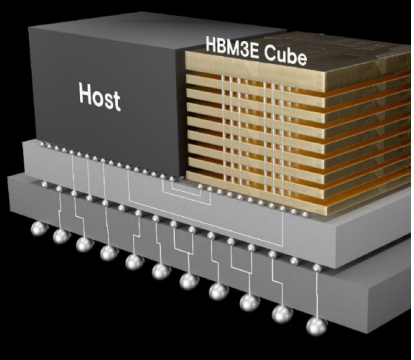

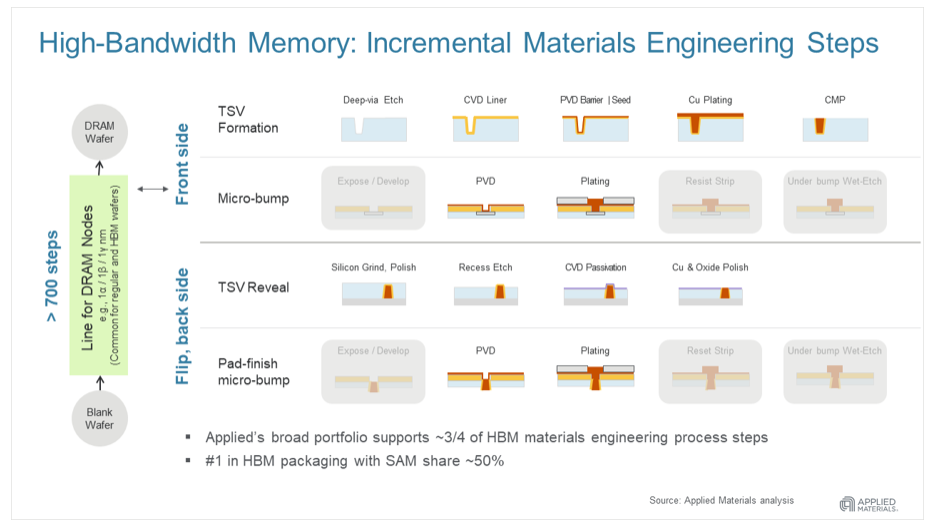

当下的HBM堆叠构造中,已融入了多达八个DRAM芯片,并且芯片制造商正筹谋在未来不久将这一数字提升至12个乃至更多。尽管DRAM芯片层面的革新至关重要,但HBM所能展现出的高密度与高带宽特性,实则得益于其先进的3D封装技术。在HBM的制造流程中,相较于制造传统DRAM所需的约700道工序,还需额外增加约19道材料工程工序。

在HBM DRAM的核心组件中,硅通孔(TSV,Through Silicon Via)扮演着举足轻重的角色——它是实现堆叠芯片间电连接的关键垂直导线。开发HBM半导体产品时遇到挑战,特别是量产时TSV技术带来的困难。

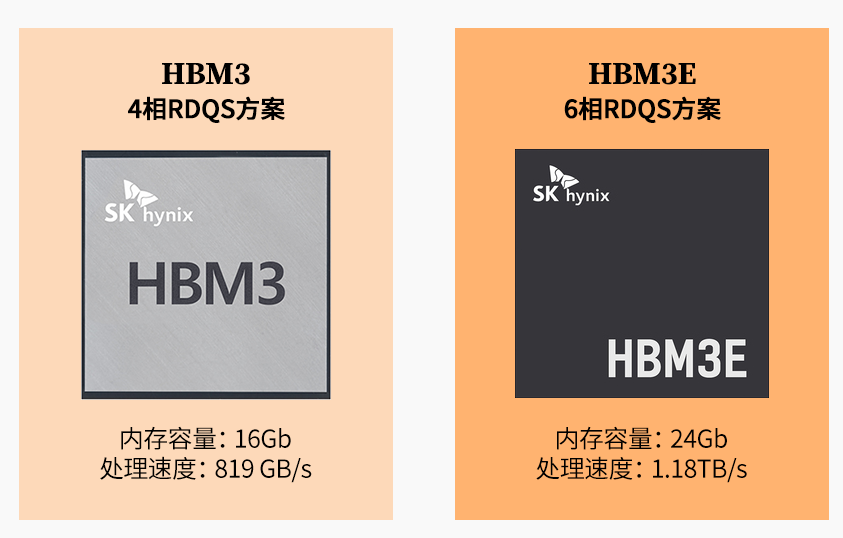

2013年SK海力士将TSV技术开发第一代HBM,该技术通过钻制微小孔洞垂直连接芯片电极,但占用了大量外围电路空间,影响产品微细化。TSV是一种先进的封装技术,通过在DRAM芯片上制造数千个微小的孔洞,实现垂直连接至电极。在HBM3E的开发过程中,SK海力士引入了创新的6相RDQS(Read-data-strobe,读数据选通)设计方案。这一全球领先的应用,使得HBM3E在保持封装尺寸不变的同时,实现了相对于上一代产品的显著性能提升。

HBM3 VSHBM3E主要规格(图片来自SK海力士)

另外,HBM的整个制造过程需历经约19项新增的材料工程挑战。在晶圆的正面加工阶段,需执行10项HBM特定工序来打造正面的互连柱与TSV,这一步骤涉及在硅片上蚀刻出沟槽,并随后用绝缘衬层与金属导线将其填满。待正面的晶圆处理作业完成后,还需将晶圆翻转至背面进行进一步的处理,此时还需再执行9项材料工程工序,以暴露出TSV并制作出背面的互连柱。

HBM逐步增加的材料工程步骤(图片来自应用材料)

TSV的技术挑战在于低热预算下创建高纵横比沟槽并衬砌。为满足HBM更高需求,新一代器件TSV数量将翻倍。TSV变窄导致沉积均匀性变差,影响性能和良率。美国应用材料公司(Applied Material)开发了新技术,能制造高纵横比TSV并提供更好覆盖。除TSV外,微凸点支柱对HBM堆叠性能也关键,但尺寸缩小会使接触电阻剧增。另一挑战是堆叠薄芯片时可能遇到的翘曲和弯曲问题。

为了应对行业面临的芯片弯曲挑战,并满足当前HBM封装的高度要求,三星HBM3E 12H采用了创新的热压非导电薄膜(TC NCF)技术。这项技术使得12层堆叠的产品在高度上与8层堆叠产品保持一致,且预示着在更高堆叠层次中将带来更大的优势。三星通过减小非导电薄膜(NCF)材料的厚度,并成功将芯片间的间隙缩小至7微米(µm),同时消除了层与层之间的任何空隙。这些改进措施使得HBM3E 12H的垂直密度相较于HBM3 8H提高了20%以上。

根据应用材料预测,为了实现更高密度的连接和更低的延迟,下一代HBM的TSV预计将从当前的5微米直径标准缩小到3微米及以下,从而导致更高的纵横比。该厂商已经证明了其工具集可以扩展到更小的尺寸和更高的纵横比,且已为各种TSV尺寸展示了其电气性能。

HBM4最新进展

标准推进

今年7月,全球微电子行业标准制定的权威机构JEDEC固态技术协会正式宣布,备受业界期待的高带宽存储器(HBM)DRAM标准的最新版本——HBM4即将完成。

HBM4作为HBM3标准的进化版,旨在进一步提升数据处理速率,同时保持其高带宽、低功耗和更大容量的核心优势。这些特点使得HBM4在高效处理大型数据集和复杂计算的应用中展现出巨大的潜力,特别是在生成人工智能(AI)、高性能计算、高端显卡和服务器等领域。

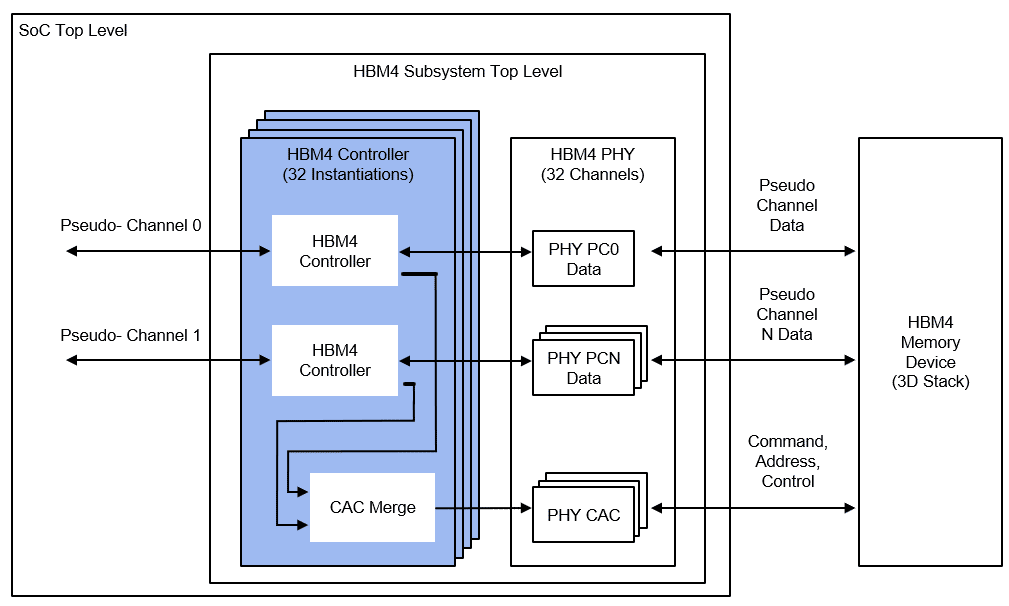

与HBM3相比,HBM4在技术上实现了多项突破。首先,HBM4将引入每堆栈两倍的通道数,这一改进将显著提升数据传输效率。其次,为了支持设备的兼容性,HBM4标准确保了单个控制器可以在需要时同时与HBM3和HBM4配合使用,从而降低了用户的升级成本。然而,由于HBM4具有更大的物理占用空间,不同的配置将需要各种插入器来适应不同的封装需求。

在技术规格方面,HBM4将指定24 Gb和32 Gb两种存储层配置,并支持4高、8高、12高和16高TSV(硅通孔)堆栈的灵活选择。这些配置将为用户提供更多的选项,以满足不同应用场景需求。此外,JEDEC固态技术协会已初步同意HBM4的最高速度为6.4 Gbps,并正在积极探讨实现更高频率的可能性,以进一步推动数据传输速率的提升。

控制器IP落地

HBM最初以1 Gb/s的数据速率问世,支持最高8层、每层16 Gb的3D堆栈。随着技术发展到HBM3,数据速率跃升至6.4 Gb/s,同时堆栈层数增至16层,每层容量达到32 Gb。目前,主流DRAM制造商已推出HBM3E,进一步将数据速率提升至9.6Gb/s。

与此同时,为了满足AI加速器和GPU对更高连接速率的需求,芯片架构师正不断推动技术革新。例如,采用六个以6.4 Gb/s运行的HBM3设备的设计,即可提供高达4.9TB/s的内存带宽。

高速芯片和内存技术授权公司Rambus的HBM3E/3内存控制器内核则进一步提升了性能,将HBM2E的信号传输速度翻倍至市场领先的9.6Gb/s(远超标准6.4 Gb/s)。该接口拥有16个独立通道,每通道64位,总数据宽度达到1024位。在最大数据速率下,每个连接的HBM3E/3内存设备可提供1.23 TB/s的总接口带宽。

为了配合HBM4标准落地和商用,Rambus于9月9日宣布推出业界首款HBM4内存控制器IP。此新解决方案支持HBM4设备的高级功能集,并将使设计人员能够满足下一代AI加速器和图形处理单元(GPU)对内存带宽的苛刻要求。

“随着大型语言模型(LLM)现在超过一万亿个参数并继续增长,克服内存带宽和容量的瓶颈对于满足人工智能训练和推理的实时性能要求至关重要。”Rambus Silicon IP高级副总裁兼总经理Neeraj Paliwal表示:“我们将推出业界首款HBM4控制器IP解决方案,以帮助客户在其最先进的处理器和加速器中实现突破性的性能。”

Rambus HBM4控制器支持每秒6.4千兆位(Gbps)的JEDEC规范。控制器还能够支持高达10Gbps的操作,为每个存储设备提供每秒2.56 TB(TB/s)的吞吐量。Rambus HBM4控制器IP可以与第三方或客户PHY解决方案配对,以实例化完整的HBM4内存子系统。

Rambus HBM4 控制器(图片来自Rambus )

对于Rambus推出业界HBM4内存控制器IP,供应链上游企业Cadence Silicon solutions group、西门子数字工业软件公司,以及半导体大厂三星电子均表示欢迎和支持。

目前,几大存储厂商除正在推进HBM3e量产进度和提升良品率,部分厂商已开始着手研发HBM4。如早些时候SK 海力士与台积电宣布共同研发HBM4基础芯片。此后,在2024年欧洲技术研讨会上,台积电确认将采用其先进的12FFC+(相当于12nm级别)和N5(5nm级别)工艺技术制造此类芯片。据台积内部人士表示“台积电与Cadence、Synopsys和Ansys等EDA合作伙伴合作,以认证HBM4通道信号完整性、IR/EM和热精度。”

另外,有最新消息透露,存储巨头三星据传计划在2026年将旗下的HBM4底层技术研发工作交由台积电承接。

本土产业链渗透

此前,长江存储成功突破3D NAND Flash芯片量产技术,让国人心潮澎湃。不过,尽管当前还无信息透露出该厂商在HBM领域的最新布局和进展情况,但是根据与其关系密切、近期正在等候IPO的武汉新芯发布的招标项目资料显示,武汉新芯计划采用三维集成多晶圆堆叠技术,旨在开发出容量更大、带宽更高、功耗更低且生产效率更高的国产高带宽存储器(HBM)产品。此举旨在推动多晶圆堆叠工艺的产业化进程,为此武汉新芯将新增约17台/套生产设备,目标是实现每月产出能力不低于3000片12英寸晶圆。根据申报稿,在三维集成领域,武汉新芯拥有国际领先的硅通孔、混合键合等核心技术。

另外,从整个产业链布局来看,中国本土企业起步虽处初级阶段,但已在半导体封测、设备及材料等领域取得实质性进展。通富微电、长电科技、深科技等封测企业,拓荆科技、赛腾股份、中微公司等设备企业,以及雅克科技、联瑞新材等材料企业,均通过自主研发或收购方式,在HBM产业链上游核心环节积极布局,不断提升技术水平和产能,为HBM产业的发展提供了有力支撑。

点击此处关注,获取最新资讯!

我的评论

最新评论